1. Introduction

High-voltage (HV) rectangular pulse generators with different architectures, designs, circuit topologies, and switch types [

1,

2,

3,

4,

5] find applications in a wide variety of electronic systems used in scientific experiments, national defense, biomedical treatments, tests, and measurements. Wide-gap semiconductor switches have excellent performance parameters. Silicon carbide (SiC) transistors are superior to their silicon counterparts in a number of aspects [

6,

7]: electrical breakdown field, thermal conductivity, saturated electron drift velocity, on-resistance, and some others.

For a field-effect transistor (FET), the gate length determines the speed characteristics and the time required for electrons to travel through the gate-driven channel. Therefore, in a comparison of different FETs, it can be expected that the switching speed of HV transistors (different manufacturers [

8,

9,

10,

11,

12,

13,

14]) decreases as the maximum blocking voltage (

Umax) and on-state current rating increase. Although these trends are possible to visualize through SPICE modeling, it is not always possible to directly compare the switching characteristics using the same computer software. There are many specialized software programs, but some of them model transistors from specific manufacturers, while using SPICE models from external sources can lead to problems and errors.

The highest

Umax of commercial SiC transistors is still below 5 kV. Examples include 3.3 kV [

12] and 4.7 kV [

13]. Identical HV transistors connected in series can provide a combination of high switching speed between OFF and ON states and high blocking voltage (

U~

N*

Umax). In stacks, series-connected transistors also demonstrate (1) a lower drain-to-source resistance in ON state, (2) a higher current density, and (3) are less susceptible to the effects of cosmic radiation compared to a single HV transistor [

15]. Stacks have a wide range of applications in the area of power electronics and converter systems. HV rectangular pulse generators belong to the mentioned areas and, in addition, fall into the subclass of high-speed instrumentation [

16,

17].

For an ideally designed stack, the slew rate of a rectangular HV pulse depends on the speed characteristics of wide-gap HV transistors that become faster and faster over time. Therefore, the design of stacks, reliable, easily, and flexibly adapted to any type of high-speed transistors, is an urgent task.

Real transistors exhibit variations in parameters; this involves well-known technical problems related to voltage imbalance on transistors [

3,

4,

5]. The perfect balance is particularly difficult to achieve in cases of high-quality HV rectangular pulses, as quasi-rectangular waveforms have a large voltage slew rate, d

U/d

t. When operating in such challenging conditions, the first transistor performing the ON→OFF transition (and the last transistor performing the OFF→ON transition) receives most of the stack voltage; this can cause the transistor to fail.

HV pulse generators exist in two basic configurations: (1) S-L-St-G and (2) S-St-L-G, where St is the stack of

N transistors, L is the resistive load, S is the HV source of power, and G is the ground node. Here, we deal with the S-L-St-G configuration, in which the decoupling capacitor eliminates the constant HV on the object of influence [

18].

There are many ways to improve the quality of HV equalization (balancing) on series-connected transistors of the same type. The combination of advantages and limitations of particular techniques is analyzed in a number of reviews [

1,

2,

3,

4,

5,

15]. For instance, in the large-scale production of HV pulse generators [

18,

19], specialized companies may employ pre-selected transistors that are not exactly identical but vary only slightly in terms of parameters. However, this approach to voltage equalization requires a large number of transistors for per-selection. This is one of the current methods for solving the voltage equalization problem.

In sophisticated gate-side methods of voltage equalization [

20], high-speed control circuits respond to HV in N×MOSFET and regulate the gates of all transistors. The complexity of setting up the entire system where the stack is in the states with large voltage slew rates on the order of 100 kV/µs limits the use of such feedback.

In practice, common approaches to voltage equalization across transistors of the same type include the use of resistive dividers, varistors, and snubbers to prevent voltage imbalance [

3,

21,

22]. These approaches also have well-known limitations [

3,

22]. In particular, there is a lack of universality in using specific chains of electronic components that respond to a certain frequency range (for example, the snubber time constant [

22]). The efficiency of known dynamic equalization methods decreases with increasing switching speed. The complexity of the problem increases significantly if the stack contains fast transistors of different types.

Some reviews [

23,

24] describe advanced methods for voltage equalization. We developed a new concept for voltage balancing for stacks with all transistors of different types. Our concept leads to the creation of innovative circuitry for HV pulse generators suited for high-speed instrumentation [

25,

26]. New generators enabled the pulsed vacuum emission of ions (electrons) from liquid metals [

25]. Such generators will find applications in our R&D for advanced superionic conductors and emission nanoionics.

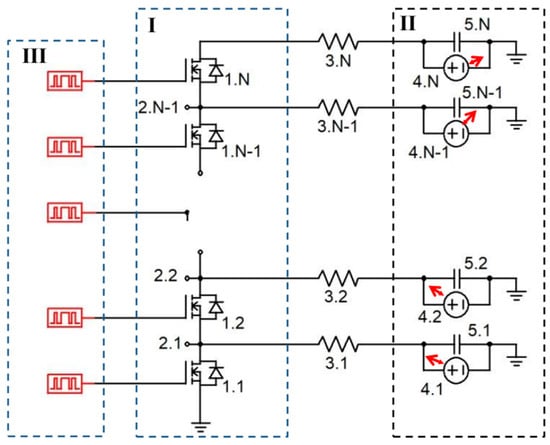

A key feature of the new HV generators is the use of several (

N) independent HV sources of power and, correspondingly,

N resistive transistor loads (as opposed to one source and one load in traditional designs [

3], see Fig. 9 in [

17]). These innovations provide reliable, fast, and high-quality voltage balancing in serial-connected transistors.

It is important to differentiate between the term “voltage equalization”, which is appropriate for stacks containing transistors of the same type, and “voltage balancing”, which more accurately describes the technical effect related to the proposed concept. Thanks to the proposed new architecture of HV pulse generators, transistors with similar dynamic characteristics but significantly different Umax can function consistently in a stack. In this context, the term “voltage equalization” refers to one particular case of voltage balancing.

The modern various SPICE software allow one to clearly prove the correctness, functionality, and usefulness of a particular circuit architecture, e.g., HV pulse generators. However, when it comes to implementing the HV circuit design in a printed circuit board (PCB) layout, some important factors for concrete customers, such as electromagnetic compatibility or the interfering influence of parasitic components, still need to be minimized.

In this study, we investigate the applicability limits of the proposed voltage balancing concept [

25,

26] by means of circuitry modeling and experimental testing. We use an original methodology of combining transistors of different types in a stack. The content of the concept becomes clear with examples of the operation of new HV generators. We identify inherent trade-offs and disadvantages of proposed innovation. Due to its simplicity, adaptability, and operational efficiency, the new technical solution has the features of basic circuits of power and HV electronics. The innovation has potential applications in the area of high-speed instrumentation.

3. Voltage/Current Distributions in Circuits of New Generators

In new generators, the mechanisms that ensure normal operation of HV transistors in the serial stack manifest themselves differently in steady-state and transient modes. Modeling of the circuit behavior allows one to find out the characteristics of switching in specific circuit architectures. The solutions of Kirchhoff equations for the electrical equivalent circuits (

Figure 2 and

Figure 3) indicate the process parameters for OFF and ON steady-states.

3.1. Equivalent Circuit with 3×MOSFET in OFF Steady-State

For the OFF state of new generators, the main interest is the voltage distribution on transistors.

Figure 2 shows the equivalent circuit of a generator in OFF state. The sources of regulated HV power (E1, E2, and E3) have effective internal resistances, depicted as r1, r2, and r3. These resistors may be about 1 MΩ. In these conditions, the E sources with voltages of about 5 kV can produce a constant current of ~5 mA. Datasheets typically provide zero gate voltage drain currents (

IDSS) for

Umax, allowing for the estimation of transistor resistances (RT1, RT2, and RT3) in OFF state. For example, STP4N150 transistors (

Umax = 1.5 kV) have

IDSS = 10

−5 A [

9], and OFF-resistors are ~10

8 Ω.

Multisim software (of 14.3 version) simulations show a high quality of voltage equalization/balancing when the stack is in OFF state: all transistors (T1, T2, and T3) with a large variation of resistance values (RT) appear to be under the same voltage.

3.2. Equivalent Circuit for New Generators in ON Steady-State

In ON state, it is necessary to maintain appropriate currents on transistors in order not to overload them. The position of Ti transistor in N×MOSFET relative to the ground node (G) determines the current (ITi) of Ti transistor. The closer the Ti transistor is to G-node, the more that current flows through it.

In HV SiC transistors, typical ON state resistances range from 0.1 to 10 Ohm. This is much lower than the transistor loads. HV sources have low effective impedances because large capacitors are connected to them in parallel. The latter provide significant pulse currents through the open channel of transistors.

Figure 3 shows the results of the electrical circuit simulation for ON steady-state (dc current) of 3×MOSFET.

The simulation results show that the currents (ITi) flowing through the transistors in 3×MOSFETs are:

i.e., IT1 current is determined by summation, even if all transistors of the stack have different resistances in ON state.

3.3. Disadvantage of Proposed Concept

Let us assume that for all HV sources (

Figure 3), the value of Ei is an integer multiple of E1 = E, where E represents the voltage difference on all transistors in a stack. If all load resistances, RL1, RL2, RL3, etc., satisfy the condition that they are equal RL, then the current IT1 through the T1 node (1) will be:

For a stack with identical

N transistors and identical loads, Equation (2) takes the form of

On the contrary, for a conventional stack (with a single load RL) under the corresponding voltage N∗E, the current IT1 is N∗E/RL, i.e., it is (N + 1)/2 times smaller than in Equation (3). Multipliers of order (N + 1)/2 are a disadvantage of the new technical solution. Therefore, the application area of the proposed concept is most likely not industrial electronics. The field of high-speed instrumental applications with their relatively low operational currents and significant demands on the quality of functional performance is promising.

3.4. Equivalent Circuit in Steady-State at Desynchronization of Transistor Switching

One of the beneficial aspects of the concept is the decreased voltage overload of the T1 transistor, which delays ON→OFF transition compared to other transistors in the stack. This is because each transistor has its own HV power source and load resistance.

Let us consider the case of 2×MOSFET stack in which the T2 transistor is in ON stationary state while T1 with

Umax = 1.5 kV is still in OFF state. The voltage overload on transistor T1 is shown in

Figure 4. This overload is 2.25 kV − 1.5 kV = 0.75 kV but not 3 kV − 1.5 kV = 1.5 kV, as it would be in a conventional generator.

The reduction in the overload results in a voltage drop across RL1 load of the T1 transistor. Therefore, in this specific case, the overload for the T1 transistor, which lags the transition from OFF to ON, is half the voltage it would be in a standard circuit with a single total load.

3.5. Equivalent Circuit at Desynchronization in Transient Switching Mode

Below, we demonstrate the high quality of voltage balancing across stack transistors during transient switching modes. The presented data relate to test experiments and circuit modeling using SPICE models of modern HV transistors. As the load resistance increases, ON→OFF transition time also increases. To verify the proposed concept in dynamic modes, we need transistors capable of fast switching between states. Information on the required transistors can be found in datasheets and by using computer SPICE models at transient circuit simulation.

The time delay for the t transistor relative to the T2 in OFF→ON transient mode (circuit as in

Figure 4) is shown in

Figure 5 for E1 = 1000 V and E2 = 2000 V. The Micro-Cap program simulates the operation of 2×STP4N150 circuit with RL1 and RL2 being 400 Ω loads. In new generators, transistor T1 is under less voltage overload than what can occur in conventional generators.

4. Modeling/Experimental Testing for Verification of Proposed Concept

To convincingly validate the proposed concept of voltage balancing, HV transistors with fast switching must be involved in modeling/experimental testing. This implies a pre-selection among different types of MOSFETs that are faster than IGBT devices.

For HV rectangular pulse generators, the design of PCB is such a complex task that it is necessary to take into account small stray capacitances and inductances to a greater extent than in the case of low-voltage (LV) electronics. If PCB is not properly designed, undesirable effects can occur in the circuit [

27], which will distort HV pulses. For example, if the pulse amplitude is 10 kV and the pulse rise time is about 10 ns, then the parasitic capacitance of 10 pF on TN transistor drain creates a current of about 5 A through the stack. Such a value is comparable to the working pulse current. In these conditions, parasitic capacitance can distort the shape of a quasi-rectangular pulse due to the overcurrent of the T1 transistor. To the best of the authors’ knowledge, among the many PCB design software, only Altium [

28] (version 25) checks PCB layouts against HV design rules.

Under these conditions, it is difficult to properly and comprehensively verify the new circuit concept in experimental tests for different types of fast transistors. Therefore, this study focuses on modeling different variants of schemes. The circuit simulation programs (such as Multisim: v. 14.3, Micro Cap: v. 12.2, LTspice: v. 24, QSpice: v. 08/16/2024, and PSIM: v. 2024.0.0247) provided tests of switching for HV SiC transistors. We also present experimental test data. For instance, experimental generators with wire connections between circuit elements in their design achieved high switching speeds with a high repetition rate.

4.1. Pre-Selection of Fast Transistors

Figure 6 and

Figure 7 show the results of the comparative modeling (LTspice). Only waveforms of SiC transistors STP4N150 (STMicroelectronics, [

9]), SCT1000N170 (STMicroelectronics) and G2R1000MT33J (GeneSiC Semiconductor [

12]) are indicated, as they were selected for experimental verification of the proposed voltage-balancing concept.

The GeneSiC [

12] offers encrypted models of transistors that are only suitable for LTspice/PLECS programs, while the new and growing Qspice program [

14] currently contains cascode models and only a few other HV transistors in its library. The selected transistors have the following characteristics: STP4N150, which is the low-cost and high-switching-speed transistor:

Umax = 1.5 kV, pulsed drain current 12 A; SCT1000N170:

Umax = 1.7 kV, pulsed drain current 20 A; and G2R1000MT33J:

Umax = 3.3 kV, pulsed drain current 10 A.

Figure 6 and

Figure 7 demonstrate that the switching of the selected HV transistors do not differ significantly in terms of rise and fall times, as well as turn-on (and turn-off) delay times. According to the simulation (

Figure 8), the slew rate of STP4N150 at turn-on is approximately equal to the same value for the SCT1000N170 transistor; the G2R1000MT33J is a better choice, while the HV IXTT1N450HV ([

13]) transistor (

Umax = 4.5 kV) shows a noticeably lower switching speed (it can be suitable for an operation at the microsecond scale).

4.2. Pre-Selection of Transistors for Experimental Stacks: New Methodology

If the proposed voltage balancing concept was tested by simulating the operation of a stack with identical transistors, the verification methodology would be considered questionable. Indeed, for identical transistors, all SPICE models are identical, and if real transistors had identical parameters, voltage balancing would not make sense at all.

Our original methodology for verifying the new concept of HV balancing in series-connected fast transistors involves modeling the behavior of stacks with transistors that are not of the same but different types. Balancing the stacks during the transitions between OFF and ON is difficult using conventional techniques based on resistors, snubber circuits, varistors, and other similar components. This is true for techniques that use gate-side controls, which need to take into account different transistor types and operating modes. In this context, the new concept has no limitations; it seems quite simple, universal, and reliable.

Figure 9 and

Figure 10 show the simulation results in LTspice (v. 24) for two new generators with different stacks.

Figure 9 corresponds to the case when one SCT10000N170 transistor is on the T1 site and G2R1000MT33J is on the T2 site. In

Figure 10, two SCT10000N170 transistors (connected in parallel) are on the T1 site, while G2R1000MT33J is on the T2 site (the circuit is shown in

Figure 11).

A comparison of

Figure 9 and

Figure 10 captures a disadvantage of new generators: the closer the transistor is to the ground node (G), the more current flows through it. To overcome this feature, we need, for example, to put two transistors at the T1 site. This will reduce the average current amplitude through each transistor, increase the pulse amplitude, and improve the shape of quasi-rectangular HV pulses. Note that if the number or type of transistors changes at the T site, new schematics enable flexible customization of the stack by adjusting resistive loads.

Component C1 (

Figure 11) symbolizes the unavoidable parasitic capacitance; it strongly affects the current flowing in high-speed switching stacks. Hence, the issue of PCB design for rectangular HV pulse generators is topical.

To show how effective the proposed concept is, we have simulated the drain voltages for a stack consisting of three very different series-connected HV transistors. The results are shown in

Figure 12.

The UF3C170400K3S transistor is a composite device in which a normally-on SiC JFET is combined with Si-MOSFET to produce a normally-off SiC-FET hybrid. In the modeled stack operation, STP4N150 transistors are on T2 and T3 sites. Note: due to the different currents on the T2 and T3 sites, the corresponding same-type transistors have different resistance at the identical voltage difference, i.e., they are in different states.

4.3. Balance Processes in Conventional Generators vs. in Proposed Concept

Let us examine in more detail the scenarios of processes involved in voltage equalization/balancing within a stack, in which transistors (T1, T2, …, TN) may exhibit differences in characteristics. Two possible cases are considered: (●) a single common load RL serves the entire stack; (●●) “individual” loads RLi serve each transistor Ti of the stack (according to the proposed concept).

(●) During the transition (most of the time t), any Ti transistor in the stack has a resistance RTi(t) significantly larger than RL. Therefore, in the specified time interval, the voltage from Ti is redistributed not to RL load but to transistors in the stack that are at earlier stages of OFF→ON transition. This process can cause the stack to break down.

(●●) If each stack transistor has its own individual RLi load, then for a long period of time during the transient process, each resistance RTi(t) satisfies the ratio: RTi(t)~RTk(t) >> RLi. In this case, transient currents flow through all loads, and the voltages are redistributed between the corresponding pairs (Ti and RLi). Such localized processes do not significantly affect each other, even if transistors block different voltages in the OFF state.

(●) In a stack with a single RL load, for any Ti and Tk transistors, RTi(t)~RTk(t) >> RL during a long part of the transition time. Therefore, the voltage redistribution occurs during the process of freeing the devices from excess charge carriers, when charges pass through the entire sequence of transistors.

(●●) If each Ti transistor in the stack has an individual load RLi << RTk(t), then the Ti transistor will be released from excess charge via RLi. This process is faster than transferring charge through a sequence of megaohm transistors, as in the case of a single common load (RL).

Thus, if all stack transistors have their own “individual” loads, then the processes of voltage redistribution in dynamic modes follow less resistive paths. The disadvantage of the proposed new solution is increased currents on transistors with small “i” indices, e.g., T1. Transistor parallelism partially solves the problem. Another disadvantage is an enhanced power consumption of multi load stacks.

6. Conclusions

The design of stacks, easily and flexibly adapted to any type of high-speed transistors, is an urgent task. The technical result from the proposed concept of reliable voltage balancing on a stack of fast high-voltage (HV) transistors creates the following advantages:

The voltage on each transistor can be very close to the nominal maximum Umax. This ensures reliable operation, enhances the amplitude of HV pulses, minimizes the rise/fall time transients, and attains a high pulse frequency.

The new circuits are simple and can be easily customized/modified to meet different requirements. The circuits can contain transistors with different Umax ratings. Transistors in parallel increase the power of pulses without changing any other parts of the circuit.

The creation of new HV pulse generators does not demand knowledge of the subtleties of the functioning of snubbers, experience in the adjustment of series-connected stacks, or skills relating to sophisticated gate-side control techniques.

The main disadvantage of new HV generators is the summation of currents flowing through all transistor loads. The closer the T transistor of the stack is to a ground (G) node, the more current flows through it. Therefore, the application area of the proposed concept is most likely not industrial electronics but rather the field of high-speed instrumentation with its relatively low operating currents and significant quality requirements for functional performance.

In this work, we only briefly examined the consequences of current flowing through a grounded (G) transistor of a stack. This current is (N + 1)/2 times larger than in a traditional technical solution. Also, issues related to connecting additional HV sources, increasing electromagnetic interference, thermal management, and circuit design complexity in terms of controlling various parasitic components have not been investigated. The ability of the new generator to provide HV pulses coupled with high currents requires further research. This includes the important question of the frequency and power limit for the proposed new HV generator architecture.

GaN discrete FETs offer outstanding speed and power, and the advances will continue to expand the frequency range and increase power level. However, there are two points to consider. First, technological progress in extremely high frequency operation is achieved by reducing the gate length in GaN devices; this path is limited for HV FETs but not for power and HV electronics based on serial-connected transistors. Second, SiC still operates at higher voltages than GaN. Therefore, in this study, we have not systematically applied the concept of HV balancing to GaN FETs. Trial simulations (LTspice, v. 24) for hybrid series-parallel stacks using three GaN GPIHV30SB5L [

10] transistors, as in

Figure 11, demonstrate a high level of voltage balancing. Switching slew rates of this hybrid stack were higher compared to a similar stack with three SiC G2R1000MT33J transistors. A total blocking voltage of 2 kV was on both types of stacks.

Overcoming and eliminating the drawbacks associated with trade-offs is the inevitable fate of any technical solution, which is never universal but fulfills with guarantee its main target functions. The proposed innovations perform their core functions excellently and will facilitate new research on yet unexplored topics. The new conception of HV balancing and generator architecture are simple, versatile, and efficient in their main functions. For this reason, the innovation has the features of basic circuits of power and HV electronics, high-speed instrumentation (for examples, see [

2,

16,

17]), and nanosecond biomedical treatments [

30,

31]. In fact, the proposed circuit can “extract” the ultimate speed characteristics from any transistor in a stack.

The significance of the proposed and verified HV balancing concept is useful to consider from different general points of view. Expert committees often have to address the relative scientific merit of findings. The article [

32] proposes a quantitative framework for such deliberations, and it argues that the degree of surprise of an experimental result is an adequate metric for evaluating the scientific merit. This thesis is consistent with [

33], that while the number of publications grows exponentially, the “cognitive extent of science” (the number of different unique concepts) increases only linearly.